FPGA/FPAA Implementation of Fractional-order Systems

Fractional Calculus (FC) has been proved through numerous research examples to be a superior tool for system description to the narrow integer order domain. This is achieved through the extra parameters introduced by allowing the differential or integral orders to take non-integer values. The promising capabilities of fractional-order devices challenge the research to find a way to simulate its behaviour until its off-shelf appearance. Different integer-order approximation techniques to the fractional-order transfer functions are investigated in the literature. There are many categories of fractional-order system approximations in analogue and digital domains, which will be investigated in this project.

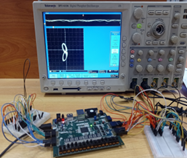

Fractional-order systems are difficult to translate into hardware as their memory dependency requires the use of high-order integer systems. FPGA technology is quite suitable for implementing complex systems. Designers are increasingly relied on the reuse of IP (Intellectual Property) cores to reduce their production cycle time and development cost. From a digital point of view, this project integrates the programmable IP core with any application and implements it in a system-on-chip (SOC) configuration. The architecture of the IP core is quite flexible and simple to integrate with the targeted applications.

Objective/Contributions:

The contribution of this work is the development of a methodology which provides practical and efficient ways to implement fractional-order systems with:

- building several PCB proto-types of emulators for the practice device using analogue approximations with an underlying approach for Field Programmable Analog Arrays (FPAA) designs as well.

- employing the investigated approximations in circuit design, such as oscillators and filters to benefit from more design tunability. Additionally, an analogue approach to FOPID control for an armature-controlled DC motor will be portrayed using existing approximations.

- designing and developing an FPGA IP core that can be used for fractional-order chaotic systems. The implemented chaotic systems will be used in image and sound encryption applications.

Outcome:

- Mohamed Walid, Menna M. Elnaggar, Wafaa S. Sayed, Lobna A. Said, Ahmed G. Radwan “A Comparative Study of Different Chaotic Systems in Path Planning for Surveillance Applications” The 2021 International Conference on Microelectronics (ICM), December 2021.

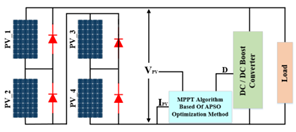

- Mahmoud F. Mahmoud , Ahmed T. Mohamed, R.A. Swief , Lobna A. Said , Ahmed G. Radwan “MPPT for A Partially Shaded PV System Using Accelerated Particle Swarms” The 2021 International Conference on Microelectronics (ICM), December 2021.