Image

Open IP cores platform

Open IP cores platform

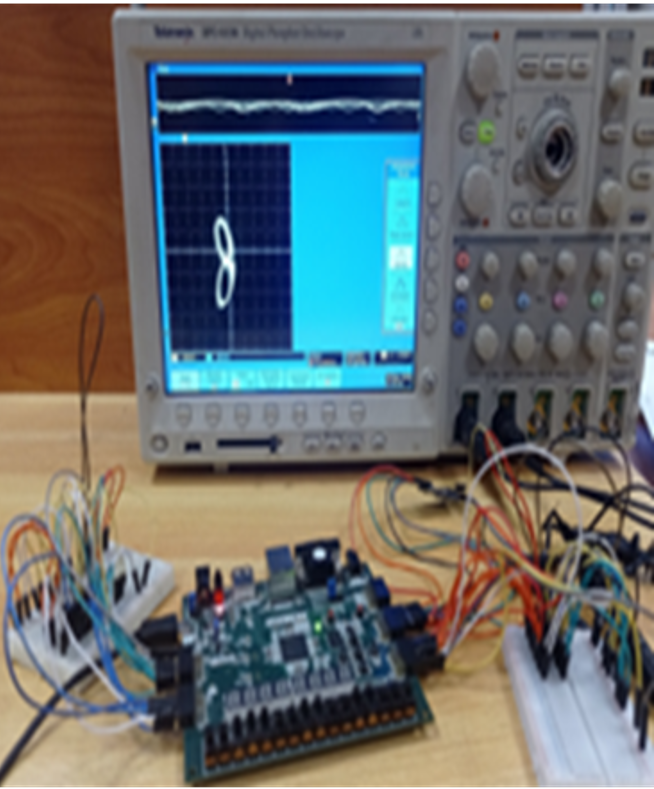

In digital design, we have implemented many hardware accelerators for many algorithms which have been validated by implementing them on FPGA. The goal of this project is to put these modules as an open source code for other researcher to reuse it. The project aims to maximize the research impact of the research done by the group by sharing the code as an open source code.

Currently running projects:

- Hardware Implementations of Information security Using Number theory and Chaotic system.

- Fractional-order Complex Chaotic Systems: FPGA Implementation and Applications.

- Efficient Implementation of Reconfigurable Machine Learning IP Cores on FPGA.

Research tracks:

-

Embedded Systems

-

IP core

-

CAD