CMOS realization of all-positive pinched hysteresis loops

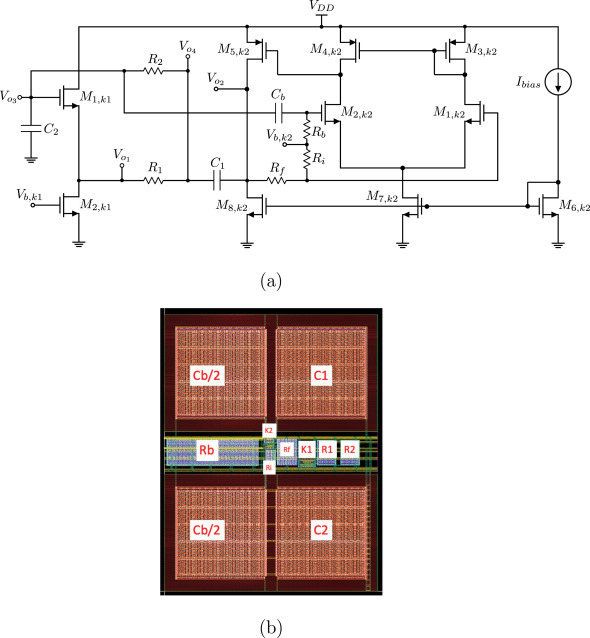

Two novel nonlinear circuits that exhibit an all-positive pinched hysteresis loop are proposed. These circuits employ two NMOS transistors, one of which operates in its triode region, in addition to two first-order filter sections. We show the equivalency to a charge-controlled resistance (memristance) in a decremental state via detailed analysis. Simulation and experimental results verify the proposed theory. © 2017 B. J. Maundy et al.