A dynamic calibration scheme for on-chip process and temperature variations

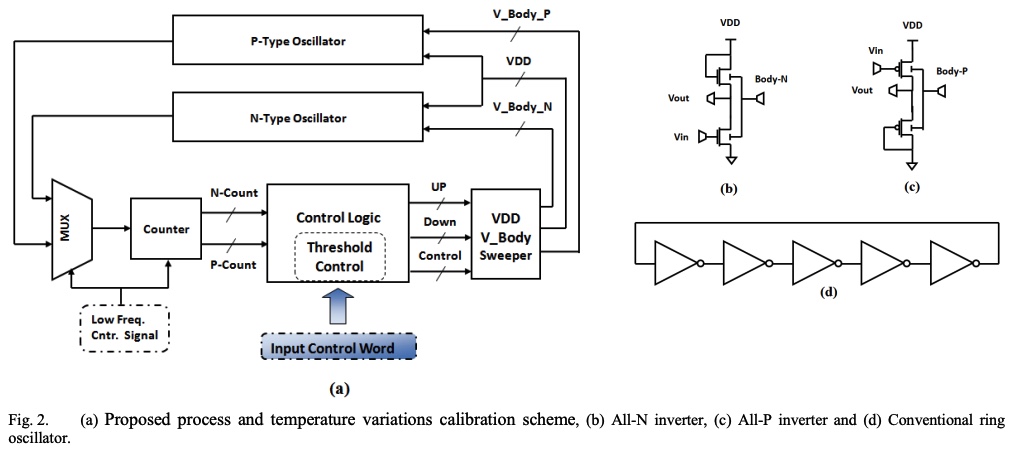

A process and temperature variation calibration scheme is proposed in this paper. The proposed system uses the supply voltage and body bias to calibrate the device parameters to match those of a certain process corner that is determined by the system designer. This scheme is characterized by its ability to dynamically change the desired mapping target according to the computational load. Moreover, the proposed system provides the ability to detect and control the n- and p-type variations independently through the use of an all-n and all-p ring oscillators. The calibration system has been implemented and simulated in TSMC 90-nm technology. Simulation results show that the system was able to reduce frequency spread (sigma) from 75 MHz to an average of 10 MHz and frequency variations from 34% to 3.1%. The results also show the system's ability to compensate for dynamic load variations. © 2011 IEEE.