Full implementation of a capacitance-to-digital converter system based on SAR logic and charge redistribution technique

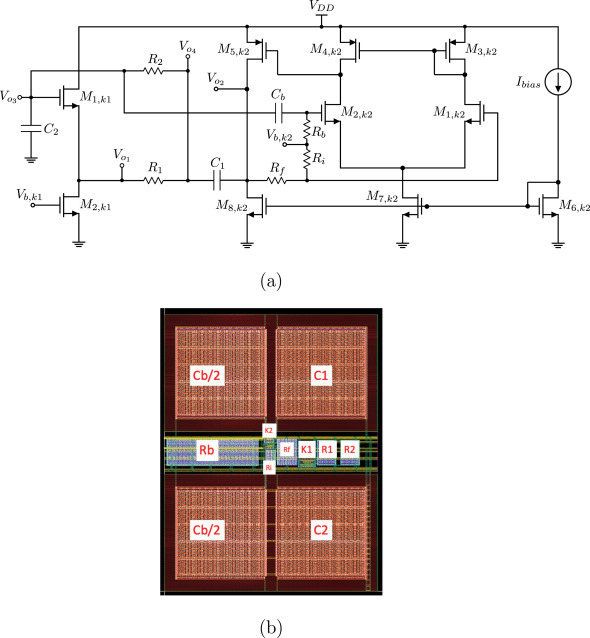

This paper demonstrates a low power 6-bit single-ended voltage-based Capacitance-to-Digital Converter (CDC) circuit based on a charge redistribution technique and Successive Approximation Register (SAR) logic operating at 370 kHz sampling rate. A proposed realization of a SAR logic control unit integrated with a low power comparator is introduced where the system blocks are entirely built on the transistor level. The system, which is fully automated with a universal clock signal, is tested for real time Cadence simulations using a 130nm model from which static and dynamic parameters are extracted. The average static and dynamic current consumption becomes in the order of 200μA using a 1.2V power supply. The tested specifications are compared with a similar CDC implementation and proved an overall enhancement and superiority on both power consumption and conversion rate performance metrics. © 2016 IEEE.