A new signaling technique for a low power on-chip SerDes transceivers

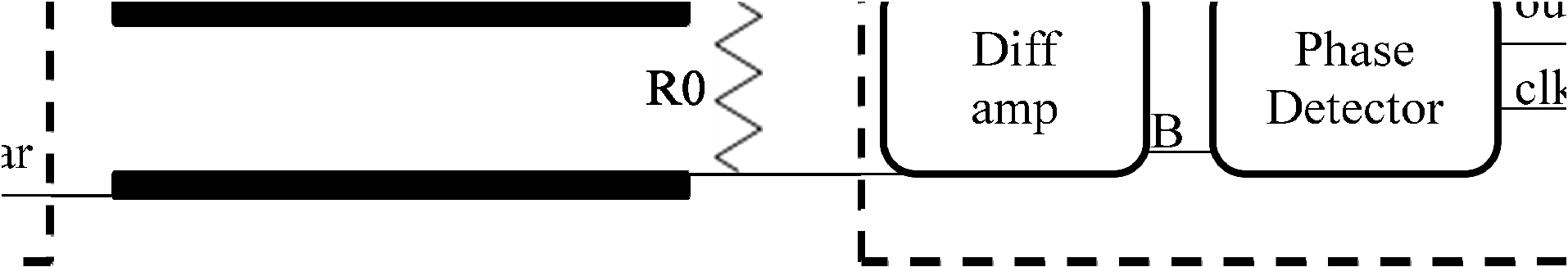

This paper represents a new self timed signaling technique for low power SerDes transceiver. A three level coding technique enables extracting the clock from the data using simple phase detector rather than using complex power hungry blocks such as Clock Data Recovery (CDR) or a Phase Locked Loop (PLL). This SerDes transceiver was implemented using 90nm TSMC technology. The transmitter serializes 8 parallel bits at 1.125GHz, and multiplexes the 10Gbps serial data stream with a 20GHz clock on a single line using three level signaling. The total power consumed in the Tx/Rx pair with the transmission line is 15 mWatt, which is very small as compared to other conventional architectures. ©2010 IEEE.