Ternary Logic Gates Design

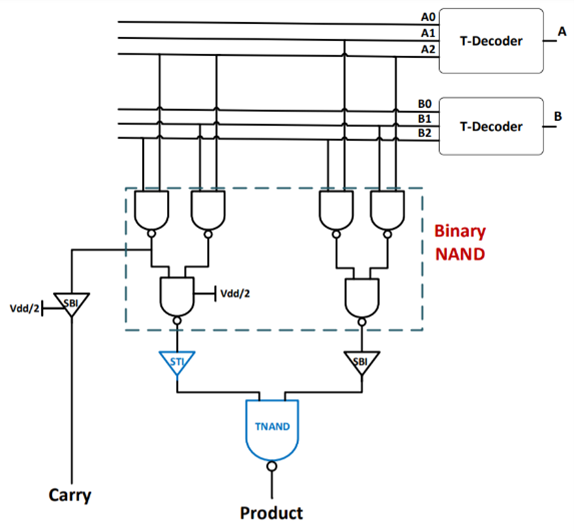

Nowadays, the demand for building CNTFET-based ternary systems has been increasing. The current two-level binary logic and MOSFET technology have been facing limitations in chip size, design complexity, and power consumption. In this proposal, the method to design Ternary logic gates based on CNTFET and Memristor is proposed. Implementing Ternary Full-Adders and Multipliers is also discussed in this proposal. Besides, the method to design Ternary sequential logic such as Latches and D-Flip-flop using carbon nano-tube field effect transistors (CNTFETS). Also, implementing ternary dynamic d-latch, N-CNTFET only based latch and proposing a new technique to build master-slave ternary D-flip-flop (DFF). Taking into consideration CNTFET exclusive feature by controlling the threshold voltage variation by changing the CNT diameter. It leads to a good and suitable alternative way for being employed in ternary logic implementation. A comparative study between the two different proposed CNTFET latches in terms of area, delay and power consumption. Moreover, comparing the master-slave DFF with other technologies show a huge improvement in power and delay. Then, we are finally able to build a full Register File and use it to build a Microprocessor such as RISC V in ternary logic.

Optimizing the data representation is considered one way to improve the overall performance of the computing systems. It was found that the natural base (e=2.71828) is the best radix from the perspective of the economy. This motivates us to consider base 3 (i.e., ternary) for digital design implementations.

Objective/Contributions:

- Literature survey of the previously published work such as logic gates and systems.

- Validation of all previously published blocks using Cadence software simulations.

- Preparing optimization flow for logic blocks, including the most important design parameters (width and length of the transistor) that affect the design performance.

- Full investigation for all different methods in n-bit ternary logic design.

- A Study for binary random access memory RAM design different techniques.

- Design a ternary RAM using the optimum simplification method.

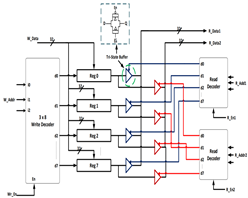

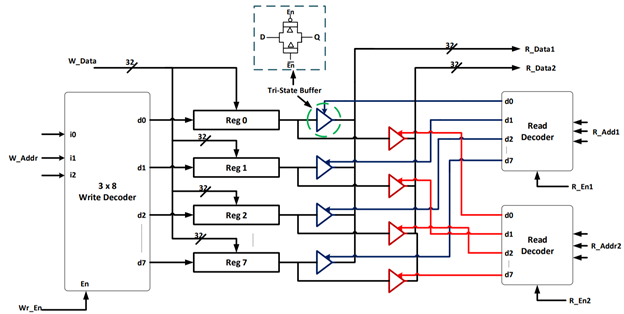

- Design a new ternary D-Flip-Flop based on a dynamic scheme to build a multi-port register file.

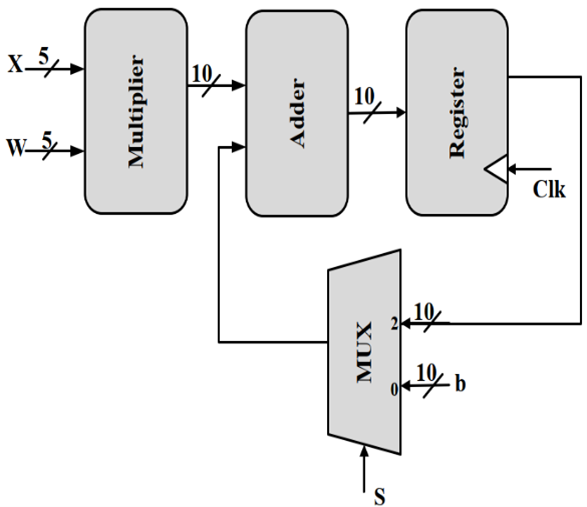

- Design and build a new Multiply-Accumulate (MAC).

- Comparison between the proposed ternary logic microprocessor and binary microprocessor results in terms of (Speed, power, and area).

Outcome:

Ternary Systems:

- Mohammaden, M. E. Fouda, I. Alouani, L. A. Said, and A. G. Radwan, “CNTFET design of a multiple-port ternary register file,” Microelectronics Journal, vol. 113, p. 105076, Jul. 2021.

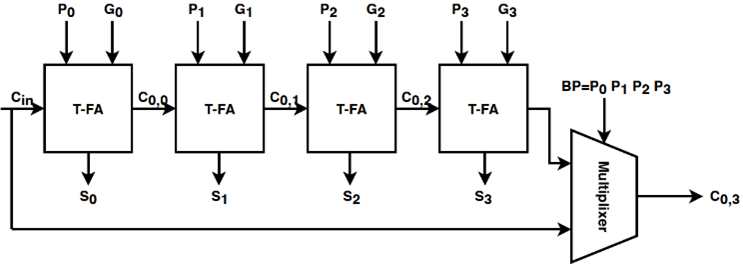

- A. Mohammaden, M. E. Fouda, L. A. Said, and A. G. Radwan, “Memristor-CNTFET based Ternary Full Adders,” 2020 IEEE 63rd International Midwest Symposium on Circuits and Systems (MWSCAS), Aug. 2020.

- M. S. Ghoneim, A. Mohammaden, R. Hesham, and A. H. Madian, “Low Power Scalable Ternary Hybrid Full Adder Realization,” 2020 32nd International Conference on Microelectronics (ICM), Dec. 2020.

Other Research Tracks (Bio-impedance):

- M. S. Ghoneim, A. Mohammaden, M. Mohsen, L. A. Said, and A. G. Radwan, “A Modified Differentiator Circuit for Extracting Cole-Impedance Model Parameters Using Meta-Heuristic Optimization Algorithms,” Arabian Journal for Science and Engineering, Apr. 2021.

- M. S. Ghoneim, A. Mohammaden, L. A. Said, Ahmed H. Madian, A. G. Radwan, and Ahmed M. Eltawil “A Comparative Study of Different Human Skin Impedance Models”, July. 2021.