High-Frequency Capacitorless Fractional-Order CPE and FI Emulator

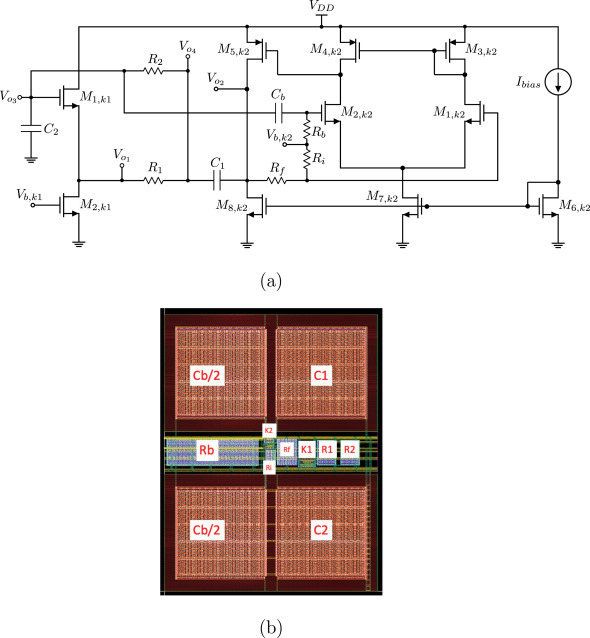

A fractional-order capacitor and inductor emulator, implemented using MOS transistors, instead of passive capacitors, is introduced in this paper. This is achieved using current mirrors as active elements, without passive resistors, and therefore reducing the circuit complexity and resulting in both a resistorless and capacitorless topology. The emulator has been designed by combining fractional-order differentiator or integrator topologies with a voltage-to-current converter. An important benefit from the design flexibility point of view is that the same topology could be used for emulating a fractional-order capacitor or inductor through an appropriate selection of the time constants and gain factors. Considering that the MOS transistors operate in the strong inversion region, it is feasible for this emulator to operate at high frequencies. The evaluation of the proposed topology has been performed using Cadence IC design suite and the Design Kit provided by the Austrian Micro Systems 0.35 μ m CMOS process. © 2017, Springer Science+Business Media, LLC.