N-digits ternary carry lookahead adder design

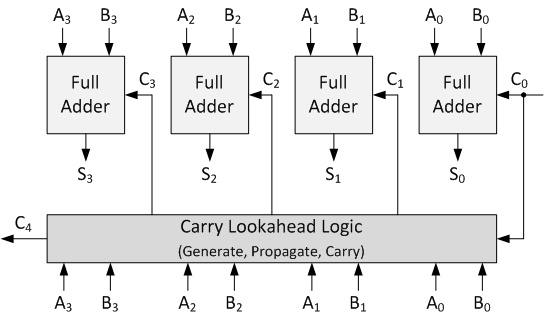

Carry lookahead adders (CLAs) are extensively used in digital circuits due to their logarithmic computational time (O(log n)) compared to linear computational time(O(n)) in the ripple carry adders. In this paper, two design approaches for N-digits ternary logic CLA based on K-map and threshold logic methods are proposed in addtion to their realization using CNTFETs only and memristor with CNTFETs. Finally, 4-bit ternary CLA is presented. A comparison and tradeoffs among the proposed designs are presented in terms of the delay and the area. The comparison shows that the transistor-only-based implementation is the best choice in the K-map design approach. However, the memristor and transistor-based implementation based on memristor and transistors integration is the best in the threshold logic (TL) design. Therefore, the proposed designs are very promising to build high performance full ternary ALU unit. © 2019 IEEE.