Breadcrumb

Energy Harvesting Management Unit for Wearable Devices

Energy harvesting materials and systems have become a popular study topic that is rapidly expanding. The harvesters will be used for a variety of applications, including distributed wireless sensor nodes for structural health monitoring, embedded and implanted sensor nodes for medical applications, recharging large system batteries, monitoring pressure in automobiles, powering unmanned vehicles, and running security systems in domestic settings. Components and devices at micro-macro sizes, spanning materials, electronics, and integration, have recently been developed. Energy harvesting has

Wastewater Treatment: Recycling, Management, and Valorization of Industrial Solid Wastes

Wastewater Treatment: Recycling, Management, and Valorization of Industrial Solid Wastes bridges the gap between the theory and applications of wastewater treatments, principles of diffusion, and the mechanism of biological and industrial treatment processes. It presents the practical applications that illustrate the treatment of several types of data, providing an overview of the characterization and treatment of wastewaters, and then examining the different biomaterials and methods for the evaluation of the treatment of biological wastewaters. Further, it considers the various types of

Indoor Air Quality Monitoring Systems for Sustainable Medical Rooms and Enhanced Life Quality

Indoor air pollution poses a substantial risk to human health and well-being, underscoring the crucial requirement for efficient monitoring systems. This paper introduces an advanced Air Pollution Monitoring System (APMS) tailored explicitly for indoor settings. The APMS integrates sensors and a user interface, ensuring the delivery of real-time and precise data concerning air quality parameters such as particulate matter (PM), volatile organic compounds (VOCs), carbon dioxide (CO2), as well as temperature and humidity. The proposed APMS has several advantages, including low maintenance

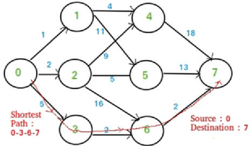

Comparison of Parallel and Serial Execution of Shortest Path Algorithms

Shortest Path Algorithms are an important set of algorithms in today's world. It has many applications like Traffic Consultation, Route Finding, and Network Design. It is essential for these applications to be fast and efficient as they mostly require real-Time execution. Sequential execution of shortest path algorithms for large graphs with many nodes is time-consuming. On the other hand, parallel execution can make these applications faster. In this paper, three popular shortest path algorithms-Dijkstra, Bellman-Ford, and Floyd Warshall-Are both implemented as serial and parallel programs

Parameter Identification of Li-ion Batteries: A Comparative Study

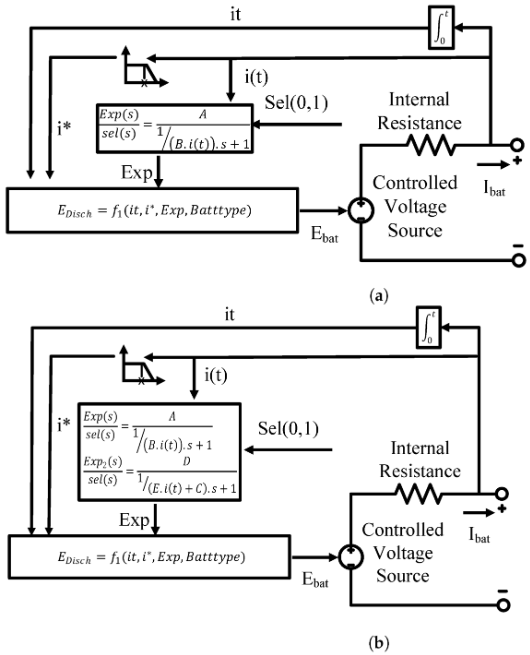

Lithium-ion batteries are crucial building stones in many applications. Therefore, modeling their behavior has become necessary in numerous fields, including heavyweight ones such as electric vehicles and plug-in hybrid electric vehicles, as well as lightweight ones like sensors and actuators. Generic models are in great demand for modeling the current change over time in real-time applications. This paper proposes seven dynamic models to simulate the behavior of lithium-ion batteries discharging. This was achieved using NASA room temperature random walk discharging datasets. The efficacy of

Microstrip Coupled Line Bandpass Filter: A Stochastic Model

Coupled line microstrip filter is regarded to be a strong contender for high frequency and wireless applications, due to its compact size, inexpensive cost, and simple engineering manufacturing. The stochastic study of the proposed microstrip filter, based on the Monte Carlo Model, presented in this paper explores the uncertainties in the microstrip filter's design parameters and their influence on the filter's functionality. The filter's microstrip thickness, lengths, and spacing are all considered as design factors. The analysis investigates the variation of the standard deviations, the mean

IoT Microchip AVR Microcontroller's Fuses and Lock Bits High Voltage Programmer

This paper proposes a reliable wireless configuration bits programmer for remotely resetting incorrectly-written Microchip AVR microcontrollers' Fuses and Lock Bits. The incorrect configuration bits programming leads critically to a micro-controller malfunction which requires correct reprogramming. The proposed programmer utilizes Wi-Fi for enabling the remote configuration bits programming via a PC or a smart mobile device. It employs the Microchip AVR High Voltage Parallel and Serial Programming protocols which uniquely support the configuration bits programming feature. The configuration

Pseudo Random Number Generators Employing Three Numerical Solvers of Chaotic Generators

Pseudo-Random Number Generator (PRNG) is required for various applications, especially cryptography. PRNGs are employed in symmetric-key algorithms, where a single key is used as a seed to the PRNG to generate a sequence of random numbers that are employed to encrypt and decrypt certain data. This work proposes a PRN G system that employs the time series generated from the numerical solution of systems of chaotic-generators Differential Equations (DEs) utilizing three different DEs solvers; Euler, Runge-Kutta 4th order, and Runge-Kutta 5th order. Various systems were solved using each of the

Novel Edge AI with Power-Efficient Re-configurable LP-MAC Processing Elements

Deep learning has become increasingly important in various fields, such as robotics, image processing, and speech recognition. However, the high computational requirements of deep learning models make it challenging to deploy them on edge & embedded devices with constrained power and area budgets. This paper proposes a novel low-power technique for implementing deep learning models on edge devices called LP-MAC (Low Power Multiply Accumulate). LP-MAC is designed for fixed-point format operations and takes advantage of reusing the input vector for MAC operations. It provides a new hardware

CPW-Fed Bow-Tie Antenna for Ambient RF Energy Harvesting Applications

This paper presents a high-efficiency bow-tie antenna for ambient RF energy harvesting at the 2.4 GHz band. Moreover, a rectifier circuit that converts the AC into DC is proposed. The antenna is fed via a CPW transmission line where a quarter wavelength transformer is inserted to match the slot bow-tie with the 50-ohm transmission line. The structure is simulated using CST software, and results are validated using HFSS. The antenna's directivity, efficiency, and bandwidth are 6.63 dBi, 89.9 %, and 0.946 GHz respectively, as simulated using CST. The antenna is fabricated on a single-layer

Pagination

- Previous page ‹‹

- Page 3

- Next page ››